4.1 介绍

偶数时钟分频很好实现,使用一个计数器累加到一定值再清零,同时翻转电平就可以了。本章主要讲的是奇数分频和小数分频。

4.2 同步整数分频器

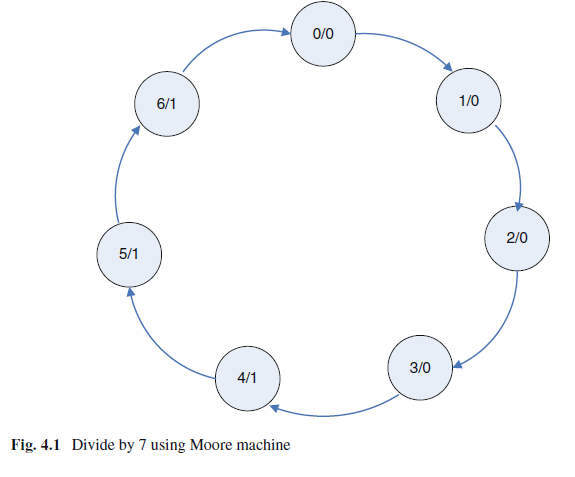

使用Moore状态机可以轻松的实现同步整数分频,需要几分频就有几种状态,但是如果是奇数分频,那么输出就不可能为50%占空比。

如图使用了一个七个状态的Moore状态机实现了7分频,其中4个状态输出为0,3个状态输出为1,显然占空比不为50%

4.3 具有50%占空比的奇数整数分频

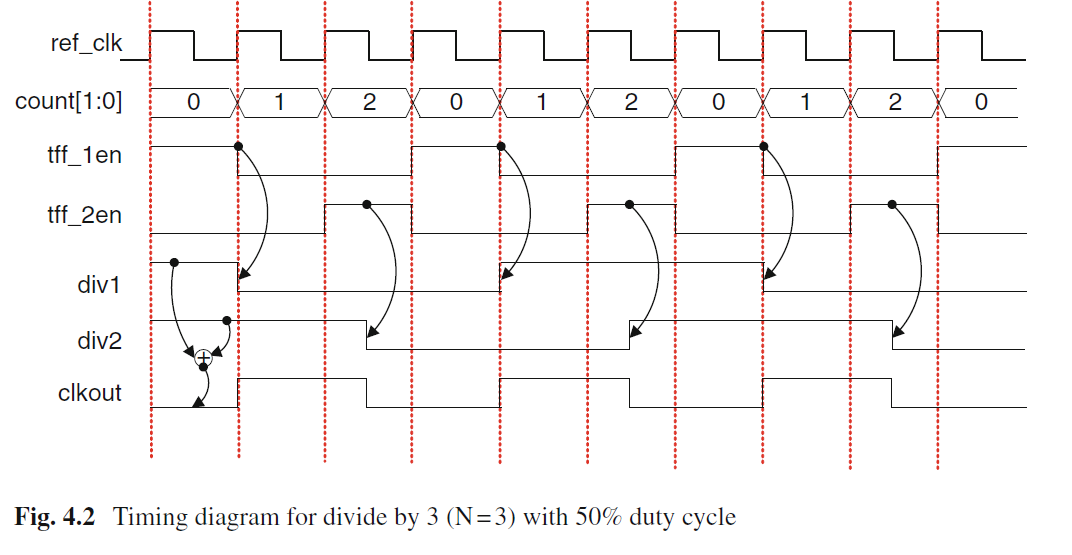

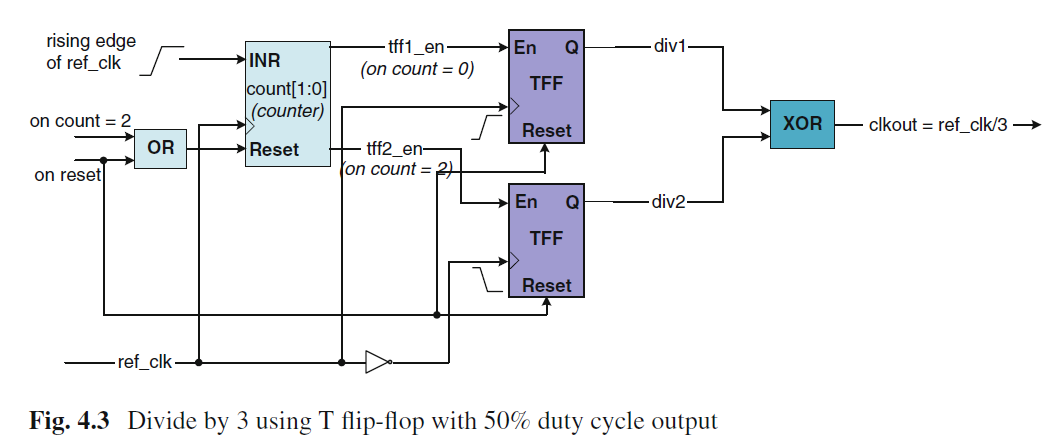

1、以期望输出频率的一半产生两个正交相位时钟(90°相位差)。

2、将两个波形异或得到输出频率。

对于整奇数N分频:

1、创建一个计数到N-1的计数器。

2、使用两个T触发器,并且第一个触发器当计数到0使能,第二个触发器计数到(N+1)/2使能。

3、TFF1由上升沿触发,TFF2由下降沿触发,两个触发器的输出都是2N分频的时钟。

4、异或得到最终输出。

`timescale 1ns / 1psmodule div3( input clk_in, input rst_n, output clk_out ); reg [3:0]count; reg div1,div2; always @(posedge clk_in or negedge rst_n) begin if(~rst_n) count <= 'd0; else begin count <= (count<2)?(count + 1'b1):'d0; end end always @(posedge clk_in or negedge rst_n) begin if(~rst_n) div1 <= 1'b0; else if(count == 0) div1 <= ~div1; end always @(negedge clk_in or negedge rst_n) begin if(~rst_n) div2 <= 1'b0; else if(count == 2) div2 <= ~div2; end assign clk_out = div1 ^ div2;endmodule

testbench

`timescale 1ns / 1psmodule tb_div3();reg clk_in;reg rst_n;wire clk_out;initial begin clk_in = 0; rst_n = 0; #100 rst_n = 1;endalways #10 clk_in = ~clk_in; div3 u0( .clk_in(clk_in), .rst_n(rst_n), .clk_out(clk_out) );endmodule

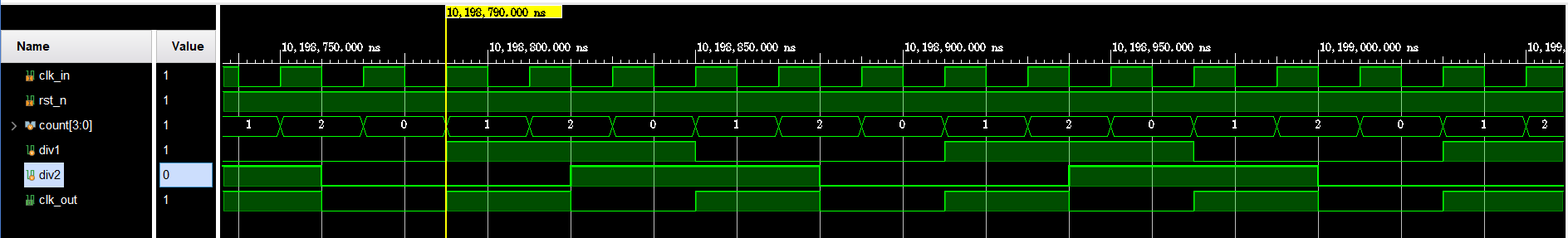

仿真波形

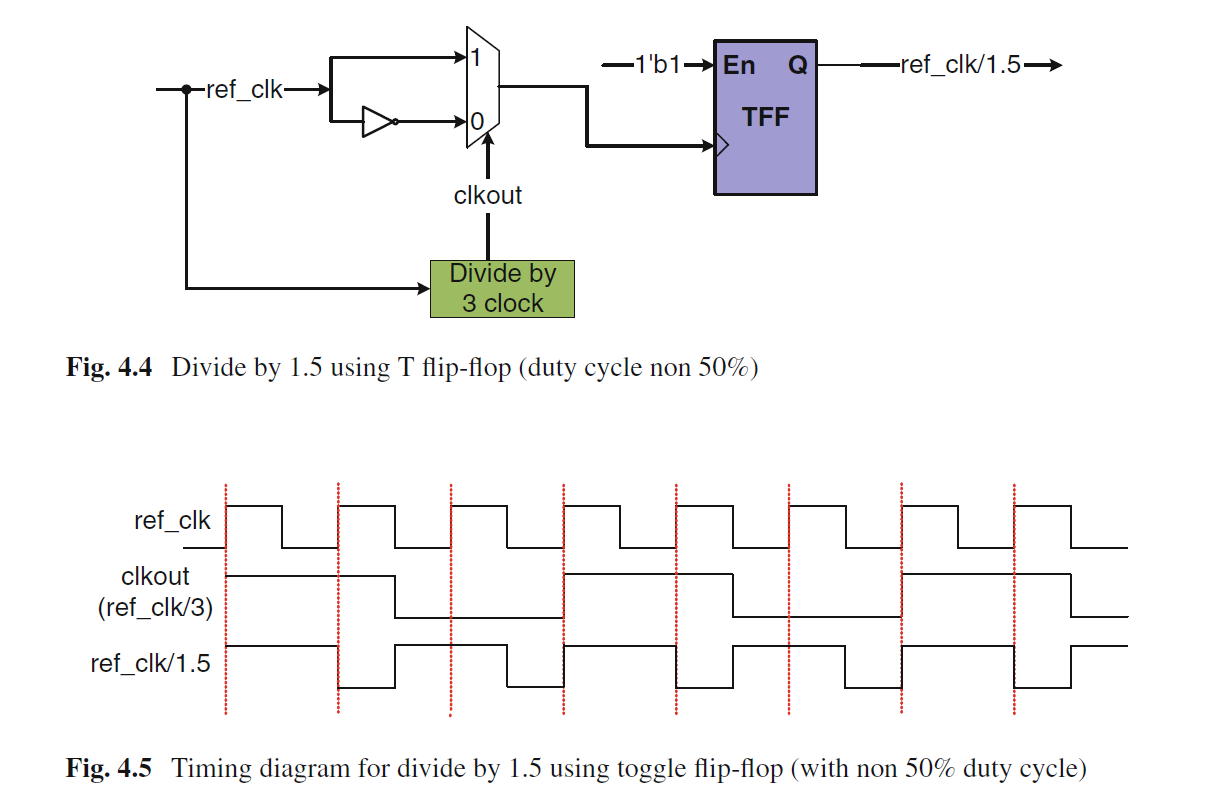

4.4 非整数分频(非50%占空比)4.4.1 具有非50%占空比的1.5倍分频

`timescale 1ns / 1psmodule div1_5( input clk_in, input rst_n, output reg clk_out);wire clk_div3;wire clk_mux;assign clk_mux = clk_div3 ? clk_in : ~clk_in;always @(posedge clk_mux or negedge rst_n) begin if(~rst_n) clk_out <= 1'b0; else clk_out <= ~clk_out;enddiv3 u0( .clk_in(clk_in), .rst_n(rst_n), .clk_out(clk_div3) );endmodule

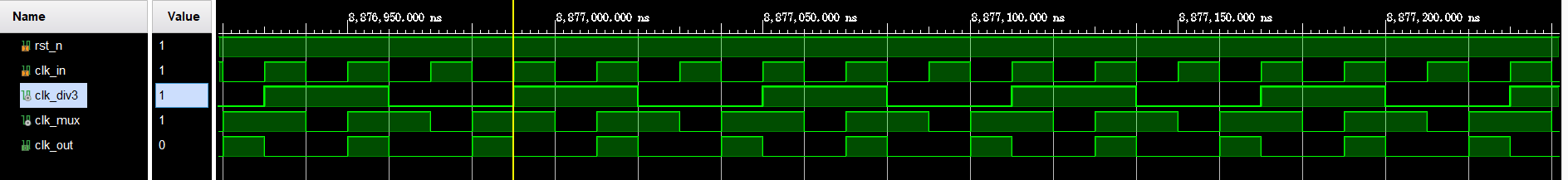

仿真波形

该电路综合可能出现问题,因为多路器的两个输入端延时并不相等,可能输出产生毛刺。参考时钟频率越高,出错的可能性也越大。

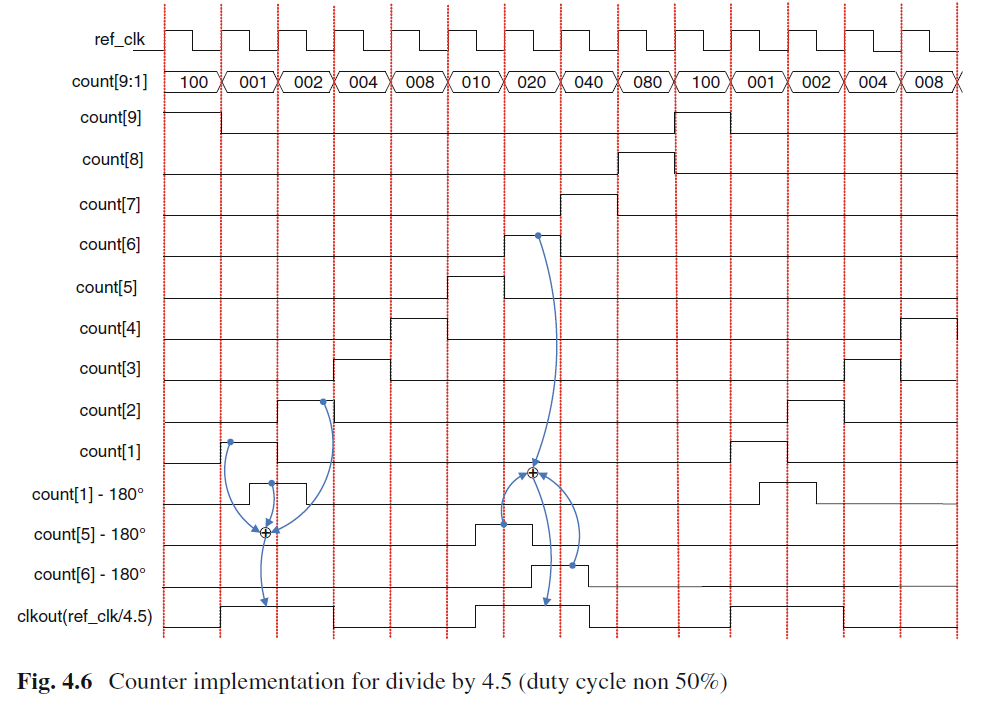

4.4.2 4.5倍分频计数器的实现(非50%占空比)

本方法可以使输出时钟不含毛刺。概括的讲,这种方法是在9个原始时钟内等间隔产生两个脉冲。

1、使用复位值为0_0000_0001的9位移位寄存器,在每个时钟上升沿循环左移一位。

2、产生第一个脉冲,下降沿移动第一位,并将移动后的结果和第一位、第二位进行或操作。

3、产生第二个脉冲,第五位和第六位半周期时移动,并与第六位进行或操作。

注意这里每一个脉冲都是三个信号相或得到的,这样做的目的是防止两个信号同时变化出现竞争冒险现象。

`timescale 1ns / 1psmodule div4_5( input clk_in, input rst_n, output clk_out);reg [8:0]count;reg count1_shift,count5_shift,count6_shift;always @(posedge clk_in or negedge rst_n ) begin if(~rst_n) count <= 'd1; else count <= {count[7:0],count[8]}; endalways @(negedge clk_in or negedge rst_n ) begin if(~rst_n)begin count1_shift <= 1'b0; count5_shift <= 1'b0; count6_shift <= 1'b0; end else begin count1_shift <= count[1]; count5_shift <= count[5]; count6_shift <= count[6]; endendassign clk_out = count[1]|count1_shift|count[2]|count5_shift|count[6]|count6_shift;endmodule

仿真波形

4.5 N分频的替换方法

以上电路都假设输入时钟占空比50%,否则小数分频输出会出现抖动,整数分频器也会有不同占空比。

基于查找表的组合反馈电路可以产生不含毛刺的时钟。

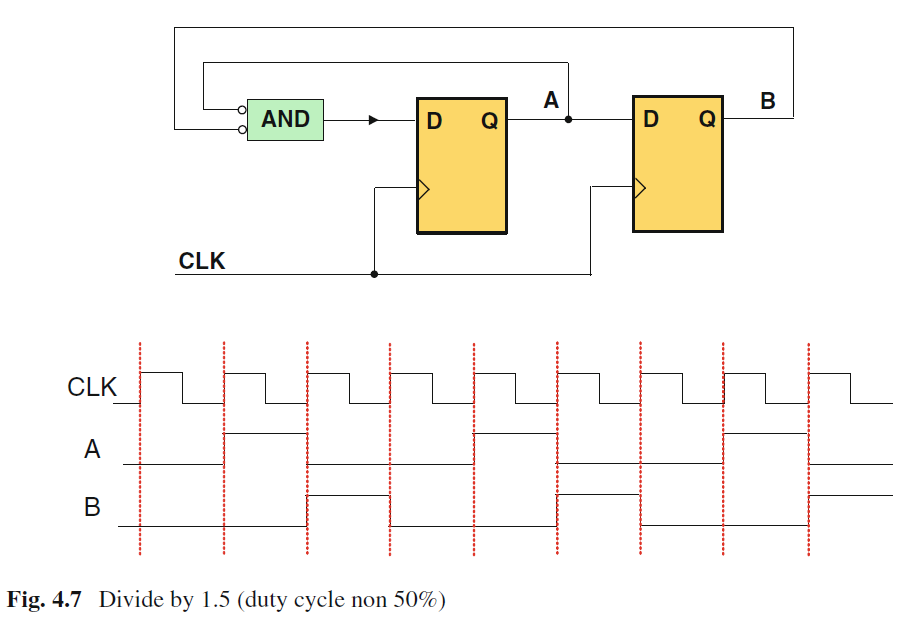

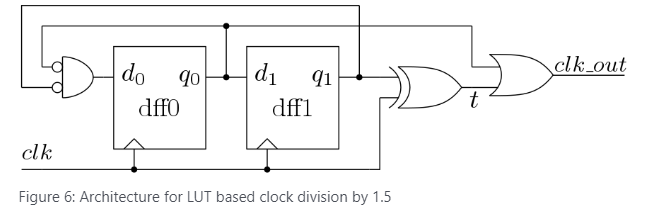

4.5.1 1.5分频的查找表实现

这里不是三分频吗,为啥说实现了一个1.5分频?

Google了一下发现作者电路没给全,完整电路如下。

这样就比较好懂了,电路也比较简单,就懒得写代码了。